芯片壓縮 集成電路設(shè)計中的關(guān)鍵技術(shù)解析

在當今高速發(fā)展的信息時代,集成電路(IC)設(shè)計正面臨著日益復(fù)雜的挑戰(zhàn)。隨著電子設(shè)備功能不斷增強,芯片的尺寸、功耗和性能優(yōu)化成為設(shè)計中的核心議題。其中,芯片壓縮技術(shù)作為集成電路設(shè)計的關(guān)鍵環(huán)節(jié),正逐漸受到行業(yè)的高度重視。

1. 芯片壓縮的概念與意義

芯片壓縮并非指物理尺寸的簡單縮小,而是指通過一系列設(shè)計優(yōu)化手段,在保證芯片性能的前提下,減少其邏輯復(fù)雜度、功耗和面積。這一技術(shù)對于提升芯片的集成度、降低生產(chǎn)成本以及延長設(shè)備續(xù)航時間具有重要意義。隨著摩爾定律的逐步逼近物理極限,芯片壓縮技術(shù)成為延續(xù)半導(dǎo)體行業(yè)發(fā)展動力的重要途徑之一。

2. 集成電路設(shè)計中的壓縮方法

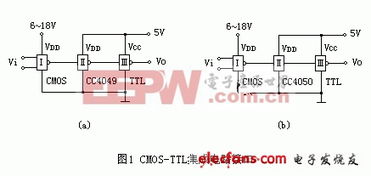

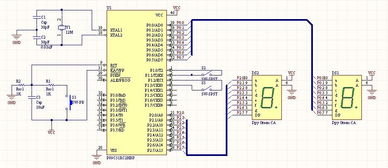

在集成電路設(shè)計流程中,芯片壓縮主要通過以下幾種方式實現(xiàn):

- 邏輯壓縮:通過優(yōu)化布爾邏輯表達式,減少邏輯門的數(shù)量,從而降低芯片的復(fù)雜度和功耗。

- 物理壓縮:在布局與布線階段,采用先進的算法優(yōu)化晶體管和連線的排布,以最小化芯片面積。

- 數(shù)據(jù)壓縮:針對存儲器模塊,應(yīng)用壓縮算法減少數(shù)據(jù)存儲空間,提升存儲效率。

- 功耗壓縮:通過動態(tài)電壓頻率調(diào)整(DVFS)、時鐘門控等技術(shù),降低芯片運行時的能耗。

3. 芯片壓縮技術(shù)的實際應(yīng)用

芯片壓縮技術(shù)已廣泛應(yīng)用于各類集成電路設(shè)計中。例如,在移動處理器領(lǐng)域,通過邏輯和物理壓縮,芯片廠商能夠在有限的空間內(nèi)集成更多功能模塊,提升處理能力的同時控制發(fā)熱和能耗。在人工智能芯片設(shè)計中,數(shù)據(jù)壓縮技術(shù)幫助優(yōu)化神經(jīng)網(wǎng)絡(luò)模型的存儲與計算,大幅提升推理效率。在物聯(lián)網(wǎng)設(shè)備中,低功耗壓縮技術(shù)使得微型芯片能夠長時間運行,推動了智能穿戴、環(huán)境監(jiān)測等場景的發(fā)展。

4. 未來發(fā)展趨勢與挑戰(zhàn)

隨著5G、人工智能、量子計算等前沿技術(shù)的興起,芯片壓縮技術(shù)將面臨新的機遇與挑戰(zhàn)。一方面,新材料(如二維材料)和新架構(gòu)(如三維集成)的出現(xiàn)為壓縮技術(shù)提供了更多可能性;另一方面,設(shè)計復(fù)雜度的增加和物理極限的逼近要求更高效的壓縮算法。跨學(xué)科合作將成為推動芯片壓縮技術(shù)創(chuàng)新的關(guān)鍵,結(jié)合機器學(xué)習(xí)、優(yōu)化理論等多領(lǐng)域知識,實現(xiàn)智能化的設(shè)計自動化工具。

芯片壓縮技術(shù)是集成電路設(shè)計中不可或缺的一環(huán)。它不僅關(guān)乎單個芯片的性能與成本,更影響著整個電子產(chǎn)業(yè)的可持續(xù)發(fā)展。通過不斷優(yōu)化壓縮方法,我們有望在有限的物理空間內(nèi)創(chuàng)造無限的計算可能,為數(shù)字化時代的進步奠定堅實基礎(chǔ)。

如若轉(zhuǎn)載,請注明出處:http://www.gojq.org.cn/product/65.html

更新時間:2026-04-14 04:09:58